# **Detector Control System of the new Muon Forward Tracker at ALICE**

Kenta Shigaki (Hiroshima University) for the ALICE Collaboration

# **ALICE Forward Upgrade in LHC Run 3**

ALICE plans major detector upgrades in LHC Run 3 from 2021. The forward muon arm will be newly equipped with a precise silicon pixel detector in front of the hadron absorber, along with a much enhanced data rate capability, to enable separation of prompt and non-prompt components of single- and di-muons and an improvement of di-muon invariamant mass resolution, as well as minimum-bias readout of Pb-Pb collisions at up to 50 kHz. New and high precision measurements will be enabled for open charm and beauty hadrons,  $J/\Psi$ ,  $\Psi$ (2S), and Y's, and low-mass di-muons, opening unique physics programs at LHC.

## **Detector Control System in ALICE Run 3**

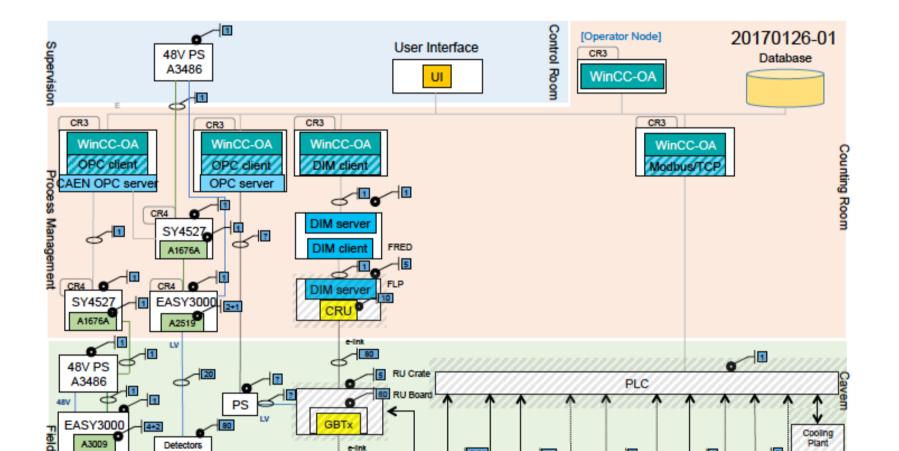

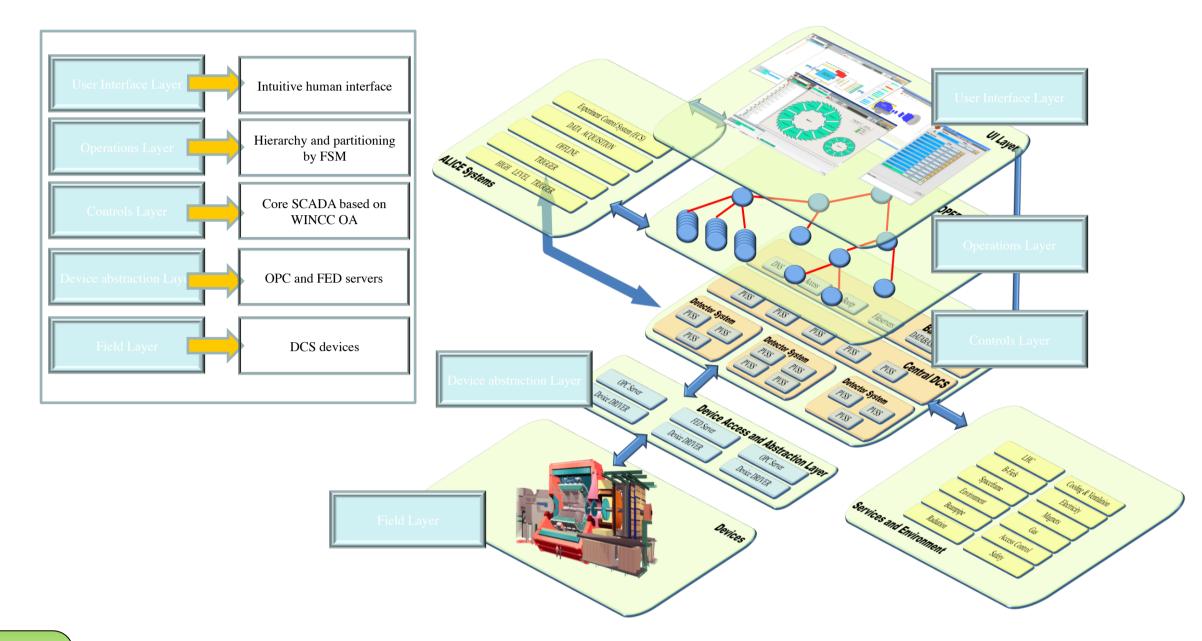

ALICE updates many of the architectures for its DCS (detector control system) in Run 3. It is a multi-layered system with the core of SCADA (supervisory control and data acquisition) based on Siemens WinCC-OA, topped with CERN JCOP (joint controls project) framework. On the lowest field layer, GBT-SCA (giga bit transfer slow control adapter) will replace ELMB (embedded local monitor board) being used for the existing detector subsystems. An additional data path exists, e.g. for status of pixel sensor chips, to be read out in the event data stream and stripped for the DCS at CRU (common readout unit).

#### **Muon Forward Tracker**

MFT (muon forward tracker) has 5 double-sided layers of silicon pixel detectors based on the MAPS technology. Each "half plane" is divided into 4 zones, which is the minimum granule for detector control such as power distribution and interlock.

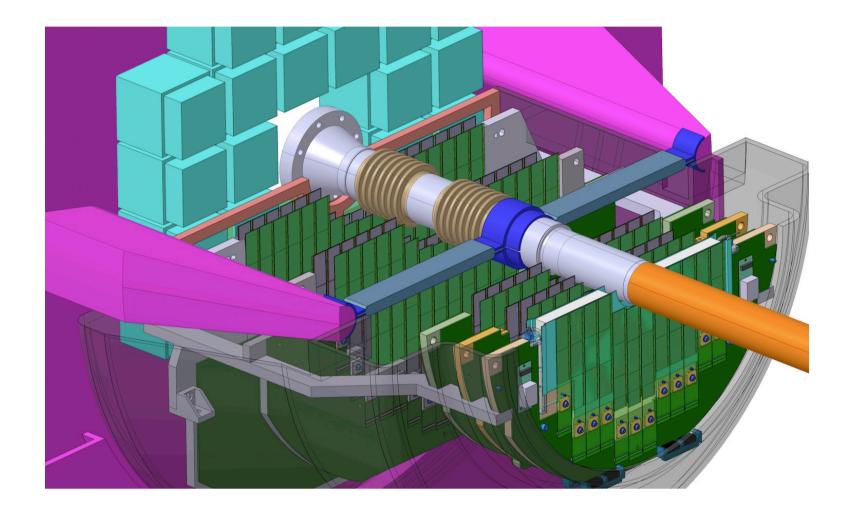

$\leftarrow$  A sketch of the lower half of MFT. It consists of 5 layers of detectors (half disks), each with 2 sensor planes (half planes) sandwiching a support structure with water cooling pipes. Half planes on the last 2 layers also carry power distribution components, such as DC-DC converters, while those for the first 3 layers are integrated on a separate power unit board.

#### **Hardware Architectures**

The hardware architecture design is summarized in the diagram on the right, called a user requirements document. The main part of the system includes control and monitoring of 3 series (for analog/digital/ bias) of low voltage power for the pixel sensors, power for the readout electronics boards, and the water cooling unit, and monitoring of various sensors and status of the pixel sensor chips (via CRU). Configuration of the chips is handled in the data

**Schematics of ALICE detector control system in Run 3. It starts with the lowest field layer** with hardware drivers, then the device abstraction layer with OPC, DIM, etc., the controls layer with SCADA on WinCC-OA, operations layer with FSM on JCOP, and finally the user interface layer.

#### **Finite State Machines**

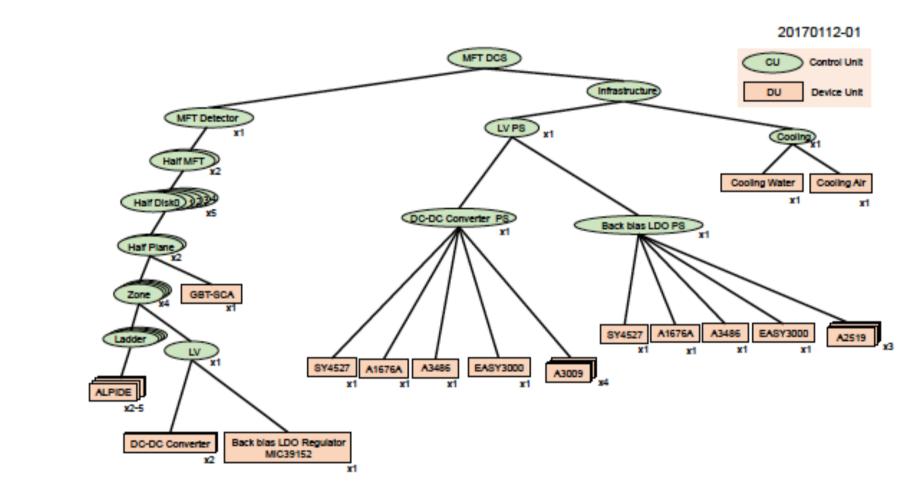

ALICE DCS is based on FSM (finite state machine) in JCOP framework. The tree structure has been identified for entire MFT, along with the state diagram of each node and their dependency.

stream apart from the DCS.

$\rightarrow$  The hardware architecture of MFT. The background colors show physical locations, e.g. inside of the ALICE detector magnet, the experimental floor, the underground counting rooms, and the control room on the surface. Each box denotes a device, with its number in small blue box. The lines are either wires, optical data links, or ethernet.

## **Test System at Hiroshima**

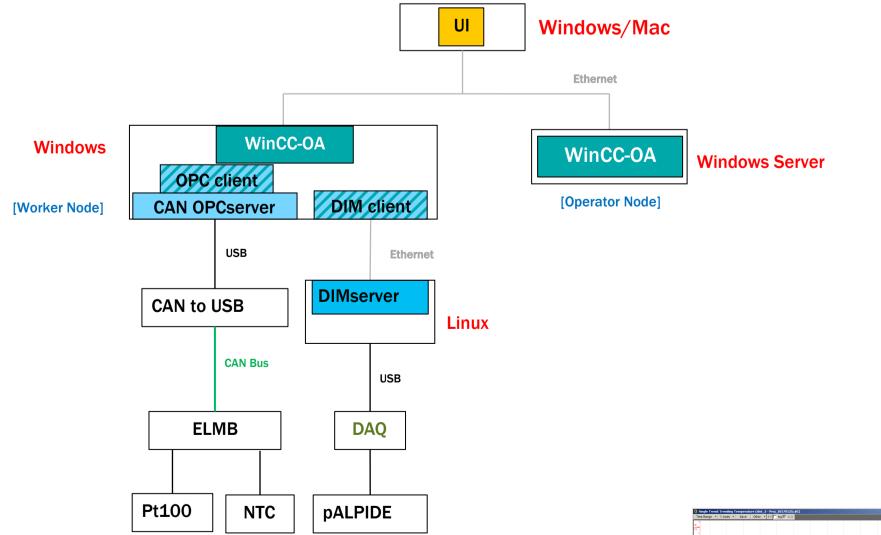

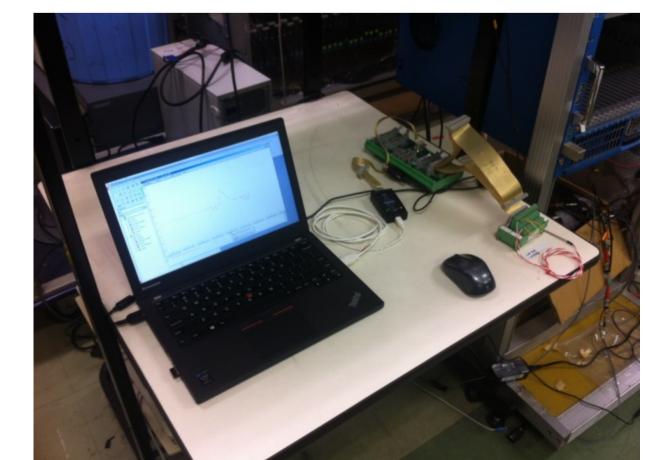

A test system of the MFT DCS has been established at Hiroshima University, Japan, with a help from the ALICE central DCS team at CERN. It is meant to be a small scale but nearly complete prototype, with multi nodes on WinCC-OA distributed project. The worker node communicates with devices via OPC (OLE for process control) and DIM (distributed information management system). An example below shows how temperature sensors on the final prototype of the pixel sensor (pALPIDEv3) are read out and monitored, mimicking the data stripping at CRU for DCS. One of the missing pieces is GBT-SCA, whose production version is not yet available as of January, 2017.

0.102 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02 01.02

**↑** The logical tree structure of MFT. The FSM nodes are categorized into control units (green ellipses) and device units (pink rectangles).

## **Implementation of Control Logics**

Implementation of FSM into JCOP framework is in progress, based on the MFT logic design. Communication between nodes has been established. FSM will be also implemented onto the DCS test system.

| JCOP Framework Devic — 🗆 🗙                                                                                                                                                                                                                                                         | 🗳 JCOP Framework Devic — 🗆 🗙                                                                                                                                                                                                                                                                                                                                    | ← FSM trees                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| )evice Manager 🛛 🥏                                                                                                                                                                                                                                                                 | Device Manager 🥏                                                                                                                                                                                                                                                                                                                                                | implemented in                                         |

| lode: Operation O Configuration                                                                                                                                                                                                                                                    | Mode: Operation Oconfiguration                                                                                                                                                                                                                                                                                                                                  | •                                                      |

| Running on: dist_1                                                                                                                                                                                                                                                                 | 2 Running on: dist_1                                                                                                                                                                                                                                                                                                                                            | JCOP framework,                                        |

| Hardware Logical FSM                                                                                                                                                                                                                                                               | 1.<br>Hardware Logical FSM                                                                                                                                                                                                                                                                                                                                      | in terms of logical                                    |

| <ul> <li>✓ Isst 1:</li> <li>✓ Isst CAEN_DCS</li> <li>✓ LVPS</li> <li>✓ A1676A</li> <li>✓ CAEN/SY4527</li> <li>✓ A1676A</li> <li>✓ CAEN/SY4527/branc</li> <li>✓ EASY3000</li> <li>✓ CAEN/SY4527/branc</li> <li>✓ A3009</li> <li>✓ A3009_ch1</li> <li>✓ CAEN/SY4527/branc</li> </ul> | <ul> <li>dist 1:</li> <li>AnalogDigital</li> <li>CAEN</li> <li>SY4527</li> <li>branchController00_A1676A</li> <li>easyCrate0_EASY3000</li> <li>easyBoard00_A3009</li> <li>channel000</li> <li>channel001</li> <li>channel002</li> <li>channel003</li> <li>channel004</li> <li>channel005</li> <li>channel006</li> <li>channel007</li> <li>channel008</li> </ul> | structure (left) and<br>hardware structure<br>(right). |

| Identity: dist_1:Manager1                                                                                                                                                                                                                                                          | channel009                                                                                                                                                                                                                                                                                                                                                      | $\rightarrow$ Synchronization                          |

| Start/Restart All     Stop All       DIM_DNS_NODE:     WinCC-PC                                                                                                                                                                                                                    | <                                                                                                                                                                                                                                                                                                                                                               | table of the top<br>node of MFT DCS in                 |

| ight click opens options                                                                                                                                                                                                                                                           | Right click opens options Close                                                                                                                                                                                                                                                                                                                                 | ICOP from owork                                        |

| — FSM trees          | Synchroniza |

|----------------------|-------------|

|                      | M FT_DCS    |

| mplemented in        | 0 F F       |

|                      | STANDBY     |

| COP framework,       | DOW NLOAI   |

| n terms of logical   | STBY_CON    |

| ii terris of logical | CALIBRATI   |

| structure (left) and | BEAM TUN I  |

|                      | MOVING_R    |

| nardware structure   | MOVING_S    |

| right)               | READY       |

| right).              | READY_LO    |

|                      |             |

|                      | ERROR       |

|                      | NO_CONTR    |

|                      | PW S_FAILU  |

|                      | IN TERLOCH  |

| → Synchronization    | IN TERLOCK  |

|                      | M IXED      |

| able of the top      |             |

|                      | EDDOD       |

| SynchronizationTable_MFT_[ | ) C S             |                  |

|----------------------------|-------------------|------------------|

| M FT_DCS                   | M FT_D etector    | Infrastructure   |

| 0 F F                      | 0 F F             | N O T_READ Y     |

| STANDBY                    | S T A N D B Y     | N O T_R EAD Y    |

| DOWNLOADING                | DOWNLOADING       | DOWNLOADING      |

| STBY_CONFIGURED            | STBY_CONFIGURED   | STBY_CONFIGURED  |

| CALIBRATING                | CALIBRATING       | STBY_CONFIGURED  |

| BEAM TUNING                | STBY_CONFIGURED   | STBY_CONFIGURED  |

| MOVING_READY               | MOVING_READY      | MOVING_READY     |

| MOVING_STBY_CONF           | MOVING_STBY_CONF  | MOVING_STBY_CONF |

| R E A D Y                  | R E A D Y         | R E A D Y        |

| READY_LOCKED               | R U N N IN G      | R E A D Y        |

|                            |                   | WARNING          |

| ERROR                      |                   | ERROR            |

| NO_CONTROL                 |                   | NO_CONTROL       |

| PW S_FAILURE               |                   | PWS_FAILURE      |

| IN TERLOCK                 |                   | IN TERLOCK       |

| IN TERLOCK_WENT            |                   | IN TERLOCK_WENT  |

| M IXED                     | M IXED            |                  |

|                            | WARNING           |                  |

| ERROR                      | ERROR             |                  |

| N O _C O N T R O L         | N O _C O N TR O L |                  |

| NTEDLOCK                   |                   |                  |

Schematics and a photo of the DCS test system at Hiroshima, based on WinCC-OA distributed project.

$\rightarrow$  A working example of the test system. Temperature of the pixel sensor prototype (pALPIDE) is read out and monitored from the operator node.

#### **Plan and Schedule**

MFT is scheduled to be installed into ALICE in LHC Long Shutdown 2 in 2019-2020. The detector construction and assembly hence shoot for finishing by the end of 2018. The DCS development is mostly planned in 2017, with an interface to the water cooling system, to be finalized in 2018, followed by installation into ALICE in 2019 and commissioning in 2020.

#### JCOP framework.

#### NTERLOCK\_WENT INTERLOCK\_WENT

## **Summary and Prospects**

ALICE Muon Forward Tracker (MFT) is a new silicon pixel detector and a part of the upgrades toward LHC Run 3 starting in 2021. Its DCS is under design and implementation based on the new architecture choices at ALICE. A test system has been established at Hiroshima University, meant to become a small scale but complete prototype. Development is in progress both on the hardware and logic fronts. A key component, GBT-SCA, is expected to arrive in the near future, to allow a complete configuration and monitoring chain. A hardware interlock is also under design, to be implemented in the existing LHC device protection system.

Presented by K.Shigaki (Hiroshima University) for the ALICE Collaboration at the 26<sup>th</sup> International Conference on Ultra-Relativistic Nucleus-Nucleus Collisions (Quark Matter 2017) in Chicago, U.S.A., on February 6 - 11, 2017